- 全部

- 默认排序

DRC问题

报错内容如下:Polygon named: Bottom Layer-No Net In net GND On 01Top Layer但是AD9却不会报此类错误,请教各位大佬这是怎么回事。

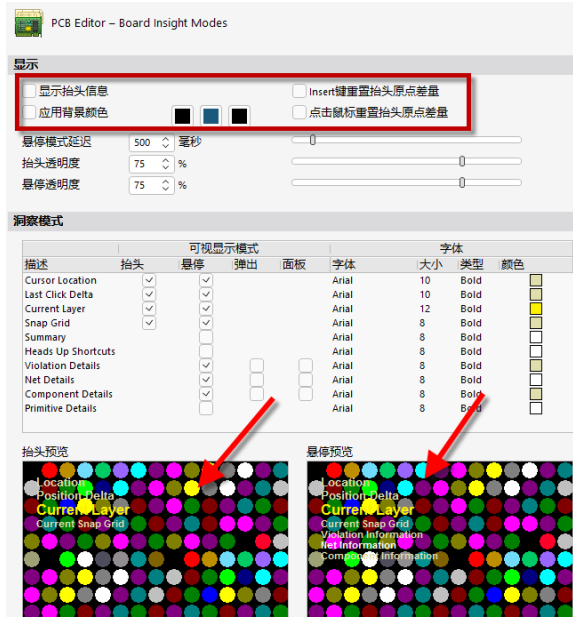

Altium Designer系统参数-显示参数的设置1、 Board Insight Modes选项卡对PCB设计者来说,去掉一些烦人的显示信息,可以有效地提高设计的可视性。一般默认的时候在PCB的左上角会有跟随鼠标移动的一些显示信息,但

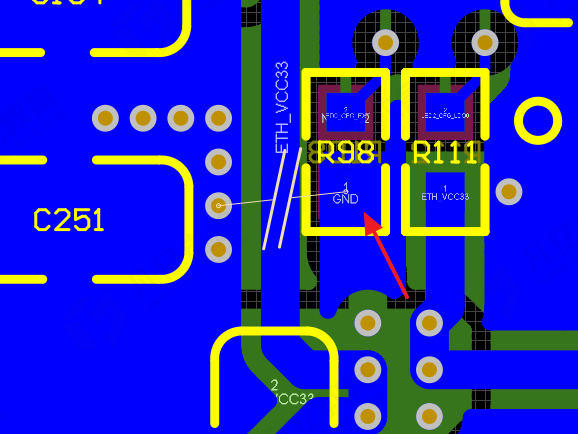

1,焊盘有开路。2.pcb存在DRC4.多处孤岛铜皮和尖岬铜皮4.走线保持3w间距4.走线避免锐角5.差分换层旁边要打地过孔6.晶振布线错误,晶振的一对线要走成类差分的形式,并整体包地处理, 线尽量短如下图8.同层连接不需要打孔9.时钟线要

对电子工程师而言,PCB的布线不仅耗时耗力,同时也非常考验工程师的真实技术水平,可以说,想做出一款优秀不错的PCB板,布线工作是不容忽视的基础环节,做好布线,除了遵循PCB规则、做好电源及地线的处理,也要关注设计规则检查(DRC)!一般来说

最近硬件工程师同行提出疑问,在硬件设计过程中layout完成后有DRC检查,已经对设计工艺规则做了检查,那么DFM可制造性分析还有必要吗?今天就为大家用一篇文章说明下DRC与DFM两者的区别。可制造性设计 (DFM) 是一种设计验证方法,与

安全间距DRC检查

安全间距DRC检查主要是检查各元素间设计的距离是否小于规则内设置的距离,若小于则会有短路风险,通过DRC检查可以将报错的位置显示出来,方便设计师进行DRC消除。进行安全间距DRC检查前,建议大家先把铜皮处理好,把所有电气层打开,将PCB整板

扫码关注

扫码关注