我的乘法已经写了好久了,但是一直改来改去,今天终于完成了算是比较标准的一个程序吧,我把所有端口的宽度都用一个变量来表示,到时候直接改动变量的值就可以了。。。

之前,我给变量赋值的语句是这么写的:

parameter e1=4'd8;///表示成数的指数位数////

parameter e2=4'd8;///表示被乘数的指数位数///

,,,,,

parameter N1=5'd32;///表示乘数总位数////

parameter N2=5'd32;//表示被乘数总的位数///

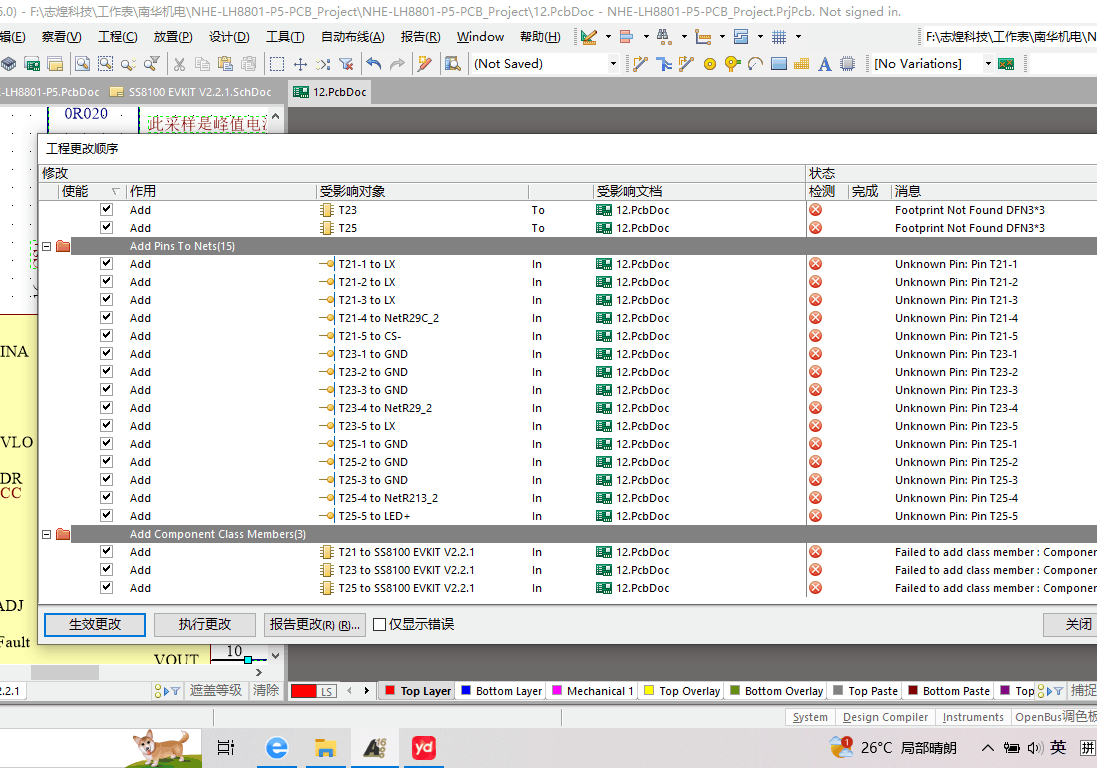

parameter O=6'd55;///表示结果的位数/////

编译的时候也没有任何错误,但是进行simulate的时候,总是出现错误,说Msb of part -selected into“in_multiplier”is out ofbounds。然后没有出现仿真的界面。后来怎么改都不正确,赋值时一位一位赋值,测试向量中数值减小,将端口宽度减小,甚至改变了一下变量名字都无济于事。

后来根据“transcript”里面的错误提示,将定义变量的程序改了一下,就是parametere1=8;其他的也都这样改,结果真的出来了,,,

其实,也有一些其他的问题,比如在主程序里面是用变量名表示端口宽度的,那么在测试向量里面也要用变量来表示端口宽度,不然在进行simulate的时候会出现warning,说主程序和测试向量里面的端口名不匹配,即Portsize (2 or 2)does not match connection size(1)for part“a”。

0

0

收藏

微博

微信

复制链接

扫码关注

扫码关注